I've been studying about CPU and I am trying to implement a small CPU, like MU0.

Control unit gets instruction and generates and gives several control signals to other parts of CPU, such as ALU, PC, ACC, etc. And I know that these works in one clock cycle.

But I have some quetions.

- Meaning of Signals (0 or 1) in Clock Cycle

Each one clock cycle has signal 1 first and has 0 next. Since CPU is an electronic equipment, 1 would mean current is flowing (so, "turn on") and 0 would mean no current flow (so, "turn off").

So, does each control signals connected to the clock cycle circuit turn off when the clock cycle is 0 at the same time, if we ignore delays of the circuit?

If not, i.e., if control signals can be 1 although clock cycle is 0, I can state my hypothesis:

Clock signal is only meaningful and only used when signal toggles 1→0 or 0→1. Control unit can not work when its signal stays in the same value since it can not recognize time is going.

Is that true or false?

- Timing to Control each Control Signals

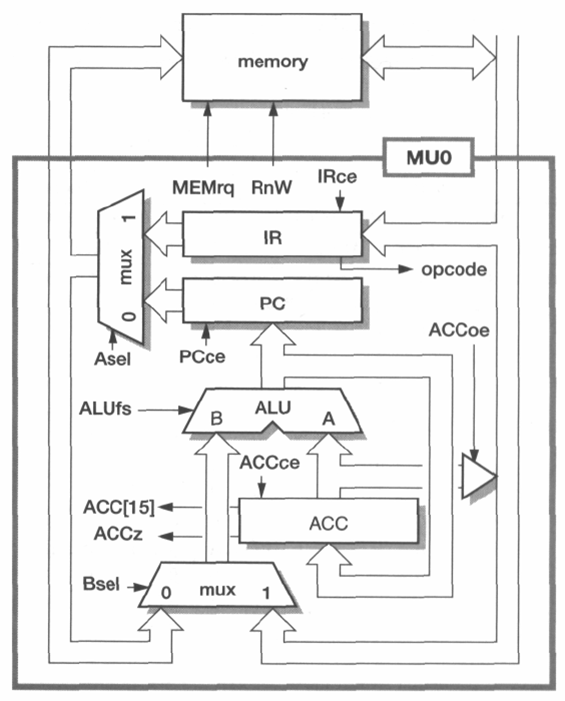

Here is the structure of MU0, one of simple CPUs.

If we want to store data from memory with the address in PC to IR and increase PC by 1 (i.e., PC = PC + 1), the manual says that setting control signals as below would do that.

- 0 : Asel, Bsel, ACCce, ACCoe

- 1 : PCce, IRce, MEMrq, RnW

- with ALU function B+1.

Note that the value of PC goes in ALU and the output of ALU is PC+1 since Asel(A selector), Bsel are 1.

But, since PCce(PC chip enabler) is 1, PC change the value by the input of PC, which is the output of ALU.

It seems good to make PC as PC+1. But my questions is:

This is an infinite loop theoritically since PC+1 would goes into ALU and PC+2 would save in PC, and then PC+2 would goes into ALU and PC+3 would save in PC, ... so and on until one clock cycle ends.

To avoid this, controlling timings would be different for each control signals. Is this really true, or is there another solution?

Thanks.

Asked By : Analysis

Answered By : Benjoyo

1.) (Almost) every component of the CPU needs to be synchronized by the clock, which means they all do their work only if the clock is high (1); never when it's low (0) (or alternatively only during rising edge). This could for example be implemented using an AND-gate, with the input to the component as first and the clock signal as second input. So the component will only get its new input if the clock is currently high, else it does nothing. And because the clock speed is set above the longest time any signal needs to propagate through any circuit in the CPU, this system is preventing signals from arriving before other signals are ready and thus keeps everything safe and synchronized. The control signals can be set at any time, but they will only be accepted during high clock.

2.) This is no loop, since the PC is actually a register which is egde triggered. This means, like mentioned above, that it is changing its state only one time per cycle for a short period of time. At an earlier time, the last output from ALU (PC + 1) is just waiting at the input of the PC. Then, at the next cycle, the PC takes its input. This is when PC = PC + 1 actually happens.

Best Answer from StackOverflow

Question Source : http://cs.stackexchange.com/questions/41024

0 comments:

Post a Comment

Let us know your responses and feedback